CMOS-Logik Grundschaltungen

# Kapitel 9: Digitaltechnik 2

- CMOS Grundschaltungen

- NOT

- NAND

- AND

- NOR

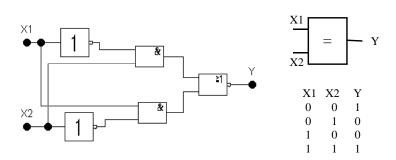

- **EXOR**

- **EXNOR**

- Laufzeiteffekte

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

9.1

N-Kanal-MOS-FET und P-Kanal-MOS-FET

Transistoren bilden die Grundlage für die Realisierung der CMOS-Logikfunktionen.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.2

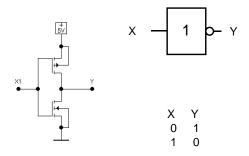

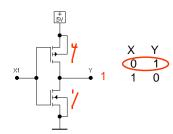

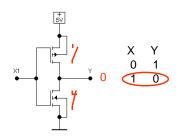

CMOS-Logik NOT

CMOS-Logik NOT

9.4

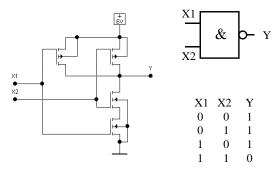

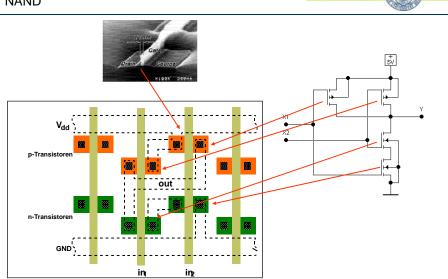

CMOS-Logik NAND

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

9.5

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.6

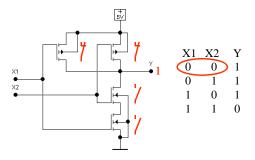

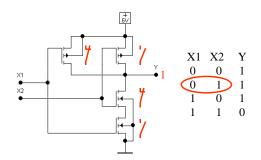

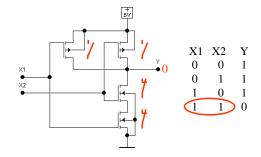

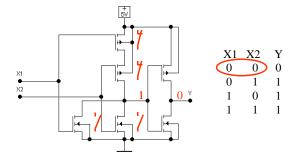

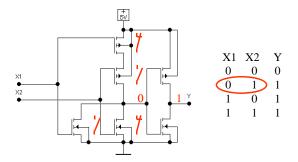

### CMOS-Logik NAND

CMOS-Logik NAND

Dr.-Ing. Achim Liers, FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.10

CMOS-Logik NAND

9.9

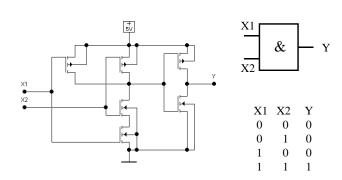

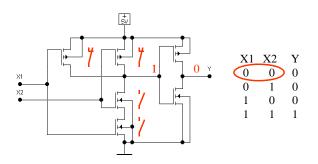

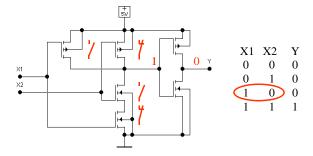

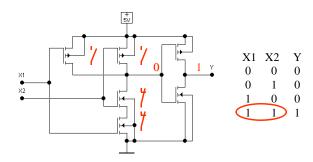

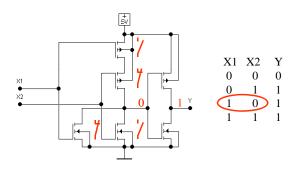

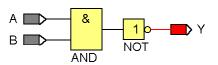

CMOS-Logik AND

X1 X2 Y

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.13

Dr.-Ing. Achim Liers, FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.14

CMOS-Logik AND

CMOS-Logik AND

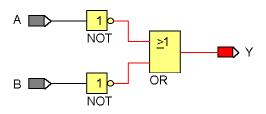

CMOS-Logik NOR

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

9.17

Dr.-Ing. Achim Liers, FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.18

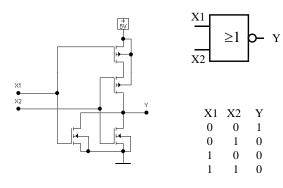

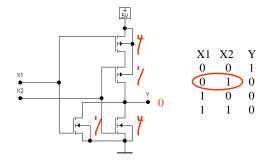

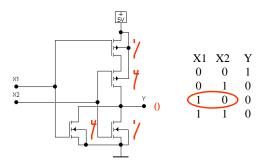

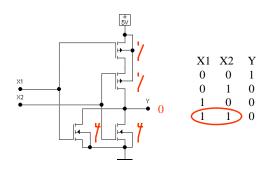

CMOS-Logik NOR

CMOS-Logik NOR

≥1

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

9.21

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.22

CMOS-Logik

CMOS-Logik

CMOS-Logik OR

Dr.-Ing. Achim Liers, FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

X1 X2 Y

0 0 0 0

0 1 1

1 0 1

1 1 1

Dr.-Ing. Achim Liers, FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

9.26

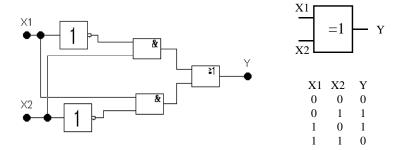

CMOS-Logik EXOR

9.25

erlin CMOS-Logik EXNOR

#### **CMOS-Familie**

| 1-le   | itet     | INV |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                 |

|--------|----------|-----|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|

| 0-gesp | errt     |     | · <del>*                                   </del>       | •.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |                 |

| A      | <u>I</u> |     | $\begin{bmatrix} & & & & & & & & & & & & & & & & & & &$ | The state of the s | +5V | В               |

| •      | <b></b>  |     |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0V  | •••••           |

|        | ļ        |     |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | U <sub>AB</sub> |

|        | -        |     |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                 |

|        | $U_{AB}$ |     |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                 |

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.29

| CMOS Logik                      | CD4000  |

|---------------------------------|---------|

|                                 | MC14    |

| Standart CMOS-Reihe             | 74C     |

| Advanced CMOS-Reihe             | 74AC    |

| Advanced CMOS-Reihe TTL-komp.   | 74ACT   |

| High-Speed CMOS-Reihe           | 74HC    |

| Low-Voltage High-Speed          | 74LV-HC |

| High-Speed CMOS-Reihe TTL-komp. | 74HCT   |

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.30

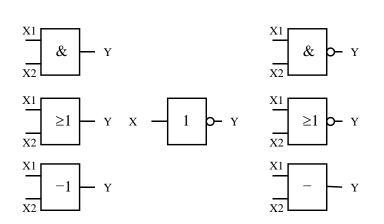

# Logikgrundbausteine

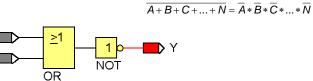

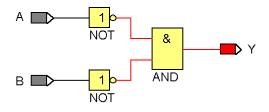

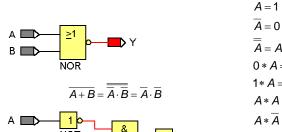

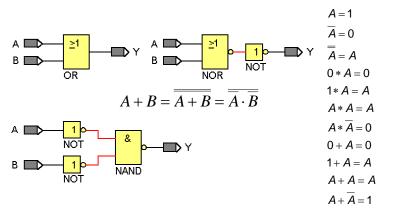

## Logikgrundbausteine Übergang OR in AND

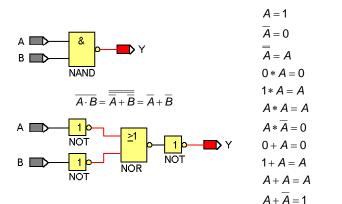

De Morgan  $\overline{A*B*C*...*N} = \overline{A} + \overline{B} + \overline{C} + ... + \overline{N}$

$\overline{A+B} = \overline{A} \cdot \overline{B}$

9.31

De Morgan  $\overline{A*B*C*...*N} = \overline{A} + \overline{B} + \overline{C} + ... + \overline{N}$  $\overline{A+B+C+...+N} = \overline{A}*\overline{B}*\overline{C}*...*\overline{N}$

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

Dr.-Ing. Achim Liers.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.33

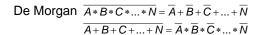

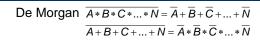

#### Logikgrundbausteine Übergang NOR in NAND

De Morgan  $\overline{A*B*C*...*N} = \overline{A} + \overline{B} + \overline{C} + ... + \overline{N}$  $\overline{A+B+C+...+N} = \overline{A}*\overline{B}*\overline{C}*...*\overline{N}$

A = A0 \* A = 0

1 \* A = AA \* A = A

$A*\overline{A}=0$ 0 + A = 0

> 1 + A = AA + A = A

$A + \overline{A} = 1$

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.34

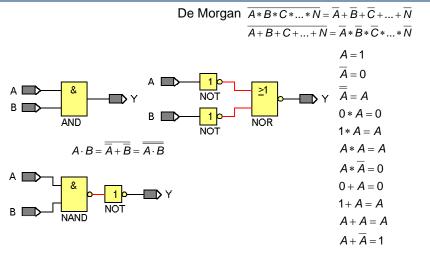

#### Logikgrundbausteine Übergang NAND in NOR

Technische Informatik I, WS10/11

# Übergang OR in NOR in NAND

## Übergang AND in NOR in NAND

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.37

# Funktionsgruppen der Logikfamilien

- ➤ Logikgrundgatter

- ➤ Logikgrundgatter mit Schmitt-Trigger Eingang

- ➤ Multiplexer / Demultiplexer

- > Register / Zwischenspeicher

- ➤ Schieberegister

- ➤Zähler / Frequenzteiler

- ➤ Monovibratoren

- ➤ Arithmetische Funktionen

- ➤ Codierer / Decodierer

- > Fehlererkennung

- ➤ Speicher / Speichersteuerung

- ➤ Bustreiber / Puffer

Dr.-Ing. Achim Liers,

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.38

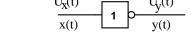

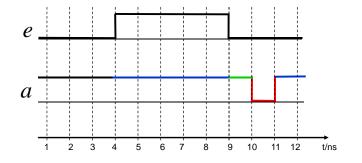

#### Laufzeiteffekte

- Auf der Gatterebene wurden die Gatter bisher als ideale logische Verknüpfungen betrachtet.

- In der Realität werden Gatter jedoch mittels Transistoren, Widerstände, Kapazitäten, etc. realisiert.

- Der zeitliche Signal-Verlauf eines realen Gatters weicht vom Verlauf der idealen booleschen Größen ab.

# Realer und idealer Signalverlauf (Inverter)

FU Berlin liers@inf.fu-berlin.de

### Realistischere Beschreibung von Gattern

- Um die Effekte auf der Gatterebene annähernd zu beschreiben, gibt es eine Reihe verschieden komplexer Modelle.

- Einfachstes Modell: Totzeitmodell

- Es werden lediglich die durch Gatter und Leitungen entstehenden Totzeiten berücksichtigt.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.41

#### Das Totzeitmodell

- Beim Totzeitmodell wird ein reales Verküpfungsglied (Gatter) modelliert durch:

- Ein ideales Verknüpfungsglied ohne Verzögerungsanteil und

- ein Totzeitglied als reines Verzögerungsglied (steht für die Schaltzeit des Gatters und ggf. für Leitungsverzögerungen).

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.42

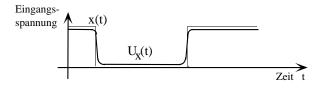

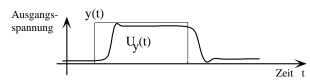

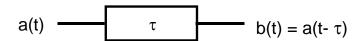

## Totzeitglied

• Das zeitliche Verhalten einer binären Größe hinter einem Totzeitglied ist dasselbe wie dasjenige vor dem Totzeitglied, aber um die Zeit τ versetzt.

# Beispiel: Totzeitmodell eines Inverters

Mit Hilfe dieses einfachen Modells lassen sich Laufzeiteffekte bereits sehr gut modellieren (auch wenn dieses Modell noch sehr idealisierend ist!).

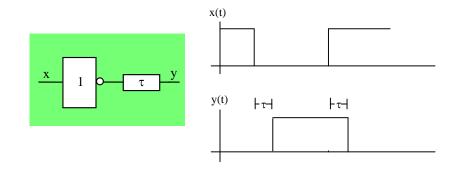

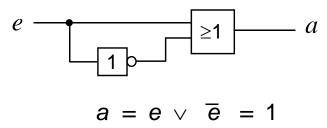

Beispiel: Inverteranwendung

# Zeit-Diagramm

Gegeben:

Beide Gatter haben eine Verzögerungszeit von 1 ns

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.45

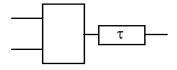

$e \xrightarrow{011000} \ge 1 \xrightarrow{\tau} \frac{111101}{\tau} a$

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.46

Verhalten eines Schaltnetzes bei Änderung der Eingabebelegung 1

- Ideales Schaltnetz:

- Das Ausgangssignal ändert sich nicht, wenn alte und neue Belegung denselben logischen Verknüpfungswert liefern.

- Das Ausgangssignal ändert sich genau einmal, wenn alte und neue Belegung verschiedene logische Verknüpfungswerte liefern.

Verhalten eines Schaltnetzes bei Änderung der Eingabebelegung 2

- Reales Schaltnetz:

- Die Änderung läuft auf verschieden langen Wegen mit verschiedenen Verzögerungen durch das Schaltnetz.

- Mehrfache Änderungen des Ausgangssignals sind möglich, bis sich der stabile Endwert einstellt

- Hasardfehler

Dr.-Ing. Achim Liers,

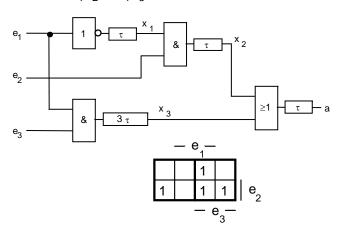

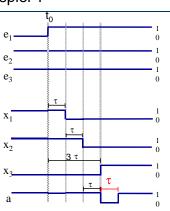

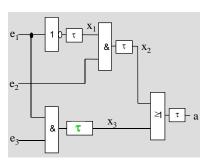

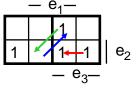

Funktion:  $a = \overline{e}_1 e_2 \vee e_1 e_3$

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.49

#### Eingabewechsel

- Es sollen die folgenden Eingabewechsel betrachtet werden:

- a) Die Eingänge e<sub>2</sub> und e<sub>3</sub> seien konstant 1, der Eingang e<sub>1</sub> wechsle von 0 auf 1

- b) Die Eingänge e<sub>2</sub> und e<sub>3</sub> seien konstant 1, der Eingang e<sub>1</sub> wechsle von 1 auf 0

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

Technische Informatik I, WS10/11

9.50

Berlin

Funktion:  $a = \overline{e}_1 e_2 \lor e_1 e_3$

# Funktionswerte bei den Übergängen:

$$(e_3, e_2, e_1) = (1,1,0)$$

$\Rightarrow$   $a = 0$

$$(e_3,e_2,e_1) = (1,1,1)$$

$$\Rightarrow$$

a = 1

$\Rightarrow$ korrektes Verhalten bei den Übergängen.

Bei beiden Übergängen darf sich der Wert von a nicht ändern. Er muss konstant 1 bleiben.

Genau dieses Verhalten kann jedoch nicht garantiert werden!

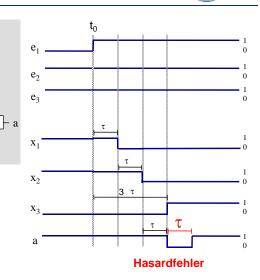

## Das Verhalten anhand des Totzeitmodells

Freie Universität

#### Das Verhalten anhand des Totzeitmodells

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I, WS10/11

9.53

#### Ergebnis

- Beim Wechsel e<sub>1</sub> von 0 auf 1 liefert das Ausgangssignal nicht ständig den korrekten Funktionswert

- + Hasardfehler

- Beim Wechsel e<sub>1</sub> von 1 auf 0 ist das Ausgangssignal hingegen korrekt

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.54

## Begriffe: Eingabewechsel, Übergang

- Definition:

- Ein Eingabewechsel ist die Änderung einer oder mehrerer Eingangsvariablen zu einem bestimmten Zeitpunkt.

- Falls sich mehrere Eingangsvariablen ändern sollen, so müssen sie dies gleichzeitig tun.

- Definition:

- Ein Übergang ist der Vorgang im Schaltnetz, der vom Eingabewechsel ausgelöst wird. Er beginnt mit dem Eingabewechsel und endet mit dem Eintreten des neuen Ruhezustandes.

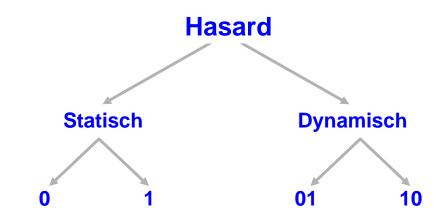

Begriffe: Hasardfehler - Hasard

- Definition:

- Ein Hasardfehler ist eine mehrmalige Änderung der Ausgangsvariablen während eines Übergangs.

- Definition:

Dr.-Ing. Achim Liers,

Ein Hasard ist die durch das Schaltnetz gegebene logisch-strukturelle Vorbedingung für einen Hasardfehler, ohne Berücksichtigung der konkreten Verzögerungswerte.

## Hasardbehaftete Übergänge 1

- Jeder Hasard ist eine Eigenschaft eines bestimmten Überganges im Schaltnetz.

- Zur Betrachtung, ob ein bestimmter Übergang hasardbehaftet ist oder nicht, interessiert nur:

- · Die logische Funktion, die durch das Schaltnetz realisiert wird.

- Die Struktur des Schaltnetzes, d.h. die Anzahl, die Verknüpfungsfunktionen und die genaue Anordnung der Gatter zur Realisierung der Funktion, nicht jedoch die tatsächlichen Verzögerungswerte der verwendeten Gatter.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.57

## Hasardbehaftete Übergänge 2

- Tritt in einem konkreten Schaltnetz bei einem bestimmten Übergang ein Hasardfehler auf, so ist dieser Übergang hasardbehaftet, also:

- Hasardfehler → Hasard

- Die Umkehrung gilt jedoch nicht: Ist ein Übergang hasardbehaftet, so folgt hieraus nicht notwendigerweise das Eintreten eines Hasardfehlers.

- Hasard ∧ ungünstige Verzögerungswerte → Hasardfehler

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.58

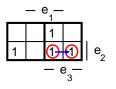

## Beispiel 1

Der Übergang  $(e_3,e_2,e_1):(1,1,0)\to(1,1,1)$  ist hasardbehaftet, da es die Möglichkeit zu einem Hasardfehler gibt.

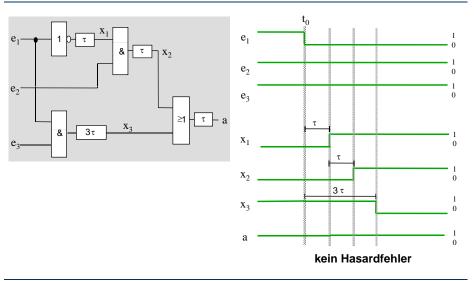

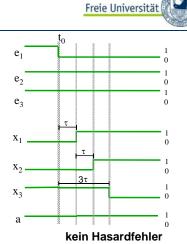

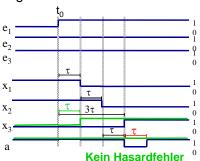

## Beispiel 2

Ändert man nun die Totzeit mit dem Wert  $3\tau$  auf den Wert  $\tau$  ab, so entsteht für den Übergang  $(1,1,0) \to (1,1,1)$  kein Hasardfehler mehr. Der Übergang ist jedoch nach wie vor hasardbehaftet, da für den Hasard konkrete Verzögerungswerte nicht interessieren.

9.59

Hasardfehler

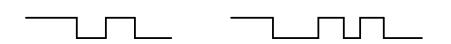

## Statischer Übergang

- Statischer Übergang:

- Ein Übergang, bei dem Anfangs- und Endwert des Ausgangssignals gleich sind (unabhängig davon, ob ein Hasardfehler eintritt oder nicht).

- Statischer 0-Übergang:

Anfangs- und Endwert des Ausgangssignal sind beide 0

- Statischer 1-Übergang:

Anfangs- und Endwert des Ausgangssignal sind beide 1

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.61

# Dynamischer Übergang

- Dynamischer Übergang:

- Ein Übergang, bei dem Anfangs- und Endwert des Ausgangssignals verschieden sind

- Dynamischen 01-Übergang:

Anfangswert des Ausgangssignals 0, der Endwert 1

- Dynamischen 10-Übergang:

Anfangswert des Ausgangssignals 1, der Endwert 0

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.62

## Beispiel

Statischer 1-Übergang:

Übergang  $(e_3, e_2, e_1)$ :  $(1,1,0) \rightarrow (1,1,1)$

Dynamischer 01-Übergang:

Übergang  $(e_3, e_2, e_1)$ :  $(0,1,1) \rightarrow (1,0,1)$

Dynamischer 10-Übergang

Übergang in umgekehrter Richtung:  $(1,0,1) \rightarrow (0,1,1)$

#### Statischer 0-Hasard

- Analog zu den Übergängen werden die Hasards als statisch bzw. dynamisch bezeichnet, je nachdem, bei welcher Art von Übergang sie auftreten.

- •

Dr.-Ing. Achim Liers,

• Ein Hasard in einem statischen 0-Übergang heißt statischer 0-Hasard.

Beispiele für statische 0-Hasardfehler:

FU Berlin liers@inf.fu-berlin.de

#### Statischer 1-Hasard

- Ein Hasard in einem statischen 1-Übergang heißt statischer 1-Hasard.

- Beispiele für statische 1-Hasardfehler:

Der Übergang  $(1,1,0) \rightarrow (1,1,1)$  im Beispiel enthält also einen statischen 1-Hasard.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de Technische Informatik I. WS10/11

9.65

#### Dynamischer 01-Hasard

- Ein Hasard in einem dynamischen 01-Übergang heißt dynamischer 01-

- Beispiele für dynamische 01-Hasardfehler:

Dr.-Ing. Achim Liers.

FU Berlin liers@inf.fu-berlin.de Technische Informatik I. WS10/11

Technische Informatik I, WS10/11

9.66

## Dynamischer 10-Hasard

- Ein Hasard in einem dynamischen 10-Übergang heißt dynamischer 10-

- Beispiele für dynamische 10-Hasardfehler:

# Klassifizierung von Hasards

#### Funktionshasard - Strukturhasard

- Weitere Unterscheidung von Hasards nach ihrer Ursache: Funktionshasards und Strukturhasards.

- Bei einem Funktionshasard liegt die Ursache in der zu realisierenden Funktion selbst.

- Bei einem Strukturhasard dagegen liegt die Ursache in der Struktur des realisierten Schaltnetzes, je nachdem welche Verknüpfungsfunktionen verwendet werden und wie sie angeordnet sind.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.69

#### **Funktionshasard**

- Definition:

- Ein Funktionshasard ist ein Hasard, dessen Ursache in der zu realisierenden Funktion liegt.

- Er tritt in jedem möglichen Schaltnetz für diese Funktion auf. Er kann nicht behoben werden.

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de

Technische Informatik I. WS10/11

9.70

#### Strukturhasard

- Definition:

- Ein Strukturhasard ist ein Hasard, dessen Ursache in der Struktur des realisierten Schaltnetzes liegt.

- Ein Strukturhasard kann deshalb immer durch Änderung der Schaltnetzstruktur bei gleicher Schaltnetzfunktion behoben werden.

- ⇒ Es ist grundsätzlich möglich, ein anderes Schaltnetz zu entwerfen, welches dieselbe Funktion realisiert und den Strukturhasard beseitigt.

## Klassifizierung von Laufzeiteffekten

| benötigt<br>man<br>Zum<br>Erkennen von | Funktion<br>des<br>Schaltnetzes | Struktur des<br>Schaltnetzes<br>(daher auch Funktion) | konkrete Verzögerungen<br>der Gatter zur gegebenen<br>Struktur des Schaltnetzes |

|----------------------------------------|---------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------|

| Funktions-<br>hasards                  |                                 |                                                       |                                                                                 |

| Struktur-<br>hasards                   |                                 |                                                       |                                                                                 |

| Funktions-<br>hasardfehler             |                                 |                                                       |                                                                                 |

| Struktur-<br>hasardfehler              |                                 |                                                       |                                                                                 |

Die dunkelgrauen Felder markieren die notwendigen Informationen Die hellgrauen Felder markieren die daraus folgenden Informationen

## Anwendungsbereites Wissen

- Realisierung in CMOS-Technik von

- NOT

- NAND

- AND

- NOR

- OR

- EXOR

- EXNOR

- Übergänge

- OR <-> AND

- NOR <-> NAND

- AND <-> NAND

- Laufzeitverhalten, Hasards

- Klassifizierung von Laufzeiteffekten

Dr.-Ing. Achim Liers,

FU Berlin liers@inf.fu-berlin.de Technische Informatik I, WS10/11

9.73